## M28F101

## 1 Mbit (128Kb x8, Bulk) Flash Memory

- 5V ±10% SUPPLY VOLTAGE

- 12V PROGRAMMING VOLTAGE

- FASTACCESS TIME: 70ns

- BYTE PROGRAMING TIME: 10µs typical

- ELECTRICAL CHIP ERASE in 1s RANGE

- LOW POWER CONSUMPTION

- Stand-by Current: 5µA typical

- 10,000 ERASE/PROGRAM CYCLES

- INTEGRATED ERASE/PROGRAM-STOP TIMER

- OTP COMPATIBLE PACKAGES and PINOUTS

- 20 YEARS DATA RETENTION

- Defectivity below 1ppm/year

- ELECTRONIC SIGNATURE

- Manufacturer Code: 20h

- Device Code: 07h

#### DESCRIPTION

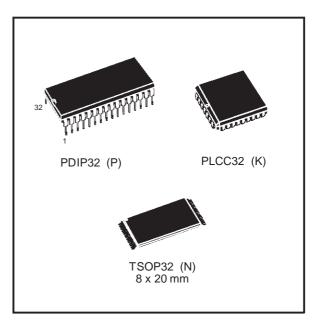

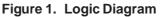

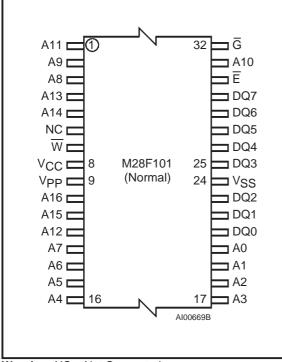

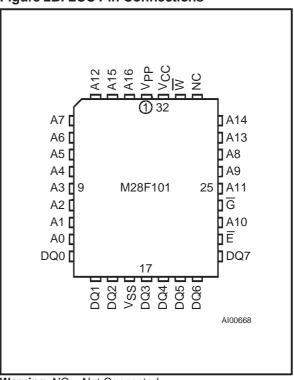

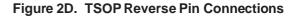

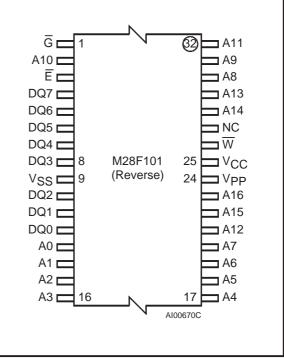

The M28F101 Flash memory is a non-volatile memory that may be erased electrically at the chip level and programmed by byte. It is organised as 128 Kbytes of 8 bits. It uses a command register architecture to select the operating modes and thus provides a simple microprocessor interface. The device is offered in PDIP32, PLCC32 and TSOP32 (8 x 20mm) packages. Both normal and reverse pinouts are available for the TSOP32 package.

#### Table 1. Signal Names

| A0-A16          | Address Inputs        |

|-----------------|-----------------------|

| DQ0-DQ7         | Data Inputs / Outputs |

| Ē               | Chip Enable           |

| G               | Output Enable         |

| W               | Write Enable          |

| V <sub>PP</sub> | Program Supply        |

| Vcc             | Supply Voltage        |

| V <sub>SS</sub> | Ground                |

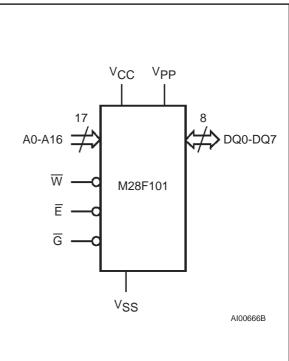

Figure 2A. DIP Pin Connections

Warning: NC = Not Connected.

Warning: NC = Not Connected.

Figure 2B. LCC Pin Connections

Warning: NC = Not Connected.

Warning: NC = Not Connected.

| Symbol                   | Parameter                                              | Value             | Unit |

|--------------------------|--------------------------------------------------------|-------------------|------|

| T <sub>A</sub>           | Ambient Operating Temperature <sup>(4)</sup>           | -40 to 125        | °C   |

| T <sub>BIAS</sub>        | Temperature Under Bias                                 | -50 to 125        | °C   |

| T <sub>STG</sub>         | Storage Temperature                                    | -65 to 150        | °C   |

| Vio <sup>(2, 3)</sup>    | Input or Output Voltages                               | -0.6 to Vcc + 0.5 | V    |

| V <sub>CC</sub>          | Supply Voltage                                         | –0.6 to 7         | V    |

| V(A9, RP) <sup>(2)</sup> | A9, RP Voltage                                         | -0.6 to 13.5      | V    |

| $V_{PP}$ <sup>(2)</sup>  | Program Supply Voltage, during Erase<br>or Programming | -0.6 to 14        | V    |

Table 2. Absolute Maximum Ratings

Notes: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

2. Minimum Voltage may undershoot to -2V during transition and for less than 20ns.

3. Maximum Voltage may overshoot to 7V during transition and for less than 20ns.

4. Depends on range.

#### **DEVICE OPERATION**

The M28F101 Flash memory employs a technology similar to a 1 Mbit EPROM but adds to the device functionality by providing electrical erasure and programming. These functions are managed by a command register. The functions that are addressed via the command register depend on the voltage applied to the V<sub>PP</sub>, program voltage, input. When V<sub>PP</sub> is less than or equal to 6.5V, the command register is disabled and M28F101 functions as a read only memory providing operating modes similar to an EPROM (Read, Output Disable, Electronic Signature Read and Standby). When V<sub>PP</sub> is raised to 12V the command register is enabled and this provides, in addition, Erase and Program operations.

#### READ ONLY MODES, $V_{PP} \leq 6.5 V$

For all Read Only Modes, except Standby Mode, the Write Enable input  $\overline{W}$  should be High. In the Standby Mode this input is don't care.

**Read Mode**. The M28F101 has two enable inputs,  $\overline{E}$  and  $\overline{G}$ , both of which must be Low in order to output data from the memory. The Chip Enable ( $\overline{E}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{G}$ ) is the output control and should be used to gate data on to the output, independant of the device selection.

**Standby Mode.** In the Standby Mode the maximum supply current is reduced. The device is placed in the Standby Mode by applying a High to the Chip Enable (E) input. When in the Standby Mode the outputs are in a high impedance state, independent of the Output Enable (G) input.

**Output Disable Mode**. When the Output Enable  $(\overline{G})$  is High the outputs are in a high impedance state.

**Electronic Signature Mode.** This mode allows the read out of two binary codes from the device which identify the manufacturer and device type. This mode is intended for use by programming equipment to automatically select the correct erase and programming algorithms. The Electronic Signature Mode is active when a high voltage (11.5V to 13V) is applied to address line A9 with E and G Low. With A0 Low the output data is the manufacturer code, when A0 is High the output is the device type code. All other address lines should be maintained Low while reading the codes. The electronic signature may also be accessed in Read/Write modes.

#### READ/WRITE MODES, 11.4V $\leq V_{PP} \leq 12.6V$

When VPP is High both read and write operations may be performed. These are defined by the contents of an internal command register. Commands may be written to this register to set-up and execute, Erase, Erase Verify, Program, Program Verify and Reset modes. Each of these modes needs 2 cycles. Eah mode starts with a write operation to set-up the command, this is followed by either read or write operations. The device expects the first cycle to be a write operation and does not corrupt data at any location in the memory. Read mode is set-up with one cycle only and may be followed by any number of read operations to output data. Electronic Signature Read mode is set-up with one cycle and followed by a read cycle to output the manufacturer or device codes.

## Table 3. Operations <sup>(1)</sup>

|                           | V <sub>PP</sub>                                                                                                                                                                                            | Operation            | Ē               | G               | w                     | A9  | DQ0 - DQ7   |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|-----------------|-----------------------|-----|-------------|

|                           |                                                                                                                                                                                                            | Read                 | VIL             | V <sub>IL</sub> | VIH                   | A9  | Data Output |

| Read Only                 | V <sub>PPL</sub>                                                                                                                                                                                           | Output Disable       | VIL             | V <sub>IH</sub> | VIH                   | Х   | Hi-Z        |

|                           |                                                                                                                                                                                                            | Standby              | V <sub>IH</sub> | Х               | Х                     | Х   | Hi-Z        |

|                           |                                                                                                                                                                                                            | Electronic Signature | Vil             | VIL             | Vih                   | Vid | Codes       |

|                           |                                                                                                                                                                                                            | Read                 | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub>       | A9  | Data Output |

| Read/Write <sup>(2)</sup> | V <sub>PPH</sub>                                                                                                                                                                                           | Write                | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> Pulse | A9  | Data Input  |

|                           | Standby     V <sub>IH</sub> X     X     X       Electronic Signature     V <sub>IL</sub> V <sub>IL</sub> V <sub>IH</sub> V <sub>ID</sub> Read     V <sub>IL</sub> V <sub>IL</sub> V <sub>IH</sub> A9     D | Hi-Z                 |                 |                 |                       |     |             |

|                           |                                                                                                                                                                                                            | Standby              | VIH             | Х               | Х                     | Х   | Hi-Z        |

Notes: 1.  $X = V_{IL}$  or  $V_{IH}$ . 2. Refer also to the Command table.

#### Table 4. Electronic Signature

| Identifier          | A0              | DQ7 | DQ6 | DQ5 | DQ4 | DQ3 | DQ2 | DQ1 | DQ0 | Hex Data |

|---------------------|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|----------|

| Manufacturer's Code | VIL             | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 20h      |

| Device Code         | V <sub>IH</sub> | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 07h      |

#### Table 5. Commands<sup>(1)</sup>

| Command                  | Cycles   |           | 1st Cycle |                                                                                                                                                                                                                                               | 2nd Cycle  |        |             |  |

|--------------------------|----------|-----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|-------------|--|

| Command                  | - Oycies | Operation | A0-A16    | X         00h         Read         00000h         20           X         90h         Read         00000h         20           X         20h         Read         00001h         07           X         20h         Write         X         20 | DQ0-DQ7    |        |             |  |

| Read                     | 1        | Write     | Х         | 00h                                                                                                                                                                                                                                           |            |        |             |  |

| Electronic               | 2        | Write     | ×         | 90h                                                                                                                                                                                                                                           | Read       | 00000h | 20h         |  |

| Signature <sup>(2)</sup> |          |           |           |                                                                                                                                                                                                                                               |            | 00001h | 07h         |  |

| Setup Erase/             | 2        | Write     | Х         | 20h                                                                                                                                                                                                                                           |            |        |             |  |

| Erase                    |          |           |           |                                                                                                                                                                                                                                               | Write      | Х      | 20h         |  |

| Erase Verify             | 2        | Write     | A0-A16    | A0h                                                                                                                                                                                                                                           | A0h Read X |        | Data Output |  |

| Setup Program/           | 2        | Write     | Х         | 40h                                                                                                                                                                                                                                           |            |        |             |  |

| Program                  |          |           |           |                                                                                                                                                                                                                                               | Write      | A0-A16 | Data Input  |  |

| Program Verify           | 2        | Write     | Х         | C0h                                                                                                                                                                                                                                           | Read       | Х      | Data Output |  |

| Reset                    | 2        | Write     | Х         | FFh                                                                                                                                                                                                                                           | Write      | Х      | FFh         |  |

57

Notes: 1.  $X = V_{IL}$  or  $V_{H}$ . 2. Refer also to the Electronic Signature table.

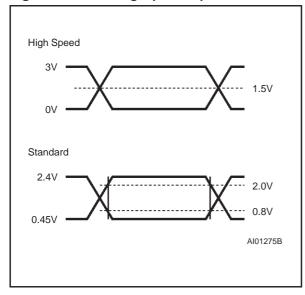

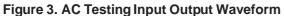

|                                       | High Speed | Standard      |

|---------------------------------------|------------|---------------|

| Input Rise and Fall Times             | ≤ 10ns     | ≤ 10ns        |

| Input Pulse Voltages                  | 0 to 3V    | 0.45V to 2.4V |

| Input and Output Timing Ref. Voltages | 1.5V       | 0.8V and 2V   |

| Table 7. | Capacitance <sup>(1)</sup> | $(T_A = 25 \ ^{\circ}C, f = 1 \ MHz)$ |

|----------|----------------------------|---------------------------------------|

|----------|----------------------------|---------------------------------------|

| Symbol           | Parameter          | Test Condition | Min | Max | Unit |

|------------------|--------------------|----------------|-----|-----|------|

| CIN              | Input Capacitance  | $V_{IN} = 0V$  |     | 6   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{OUT} = 0V$ |     | 12  | pF   |

Note: 1. Sampled only, not 100% test.ed

#### READ/WRITE MODES (cont'd)

Awrite to the command register is made by bringing  $\overline{W}$  Low while  $\overline{E}$  is Low. The falling edge of  $\overline{W}$  latches Addresses, while the rising edge latches Data, which are used for those commands that require address inputs, command input or provide data output.

The supply voltage  $V_{CC}$  and the program voltage  $V_{PP}$  can be applied in any order. When the device is powered up or when  $V_{PP}$  is  $\leq 6.5V$  the contents of the command register defaults to 00h, thus automatically setting-up Read operations. In addition a specific command may be used to set the command register to 00h for reading the memory.

The system designer may chose to provide a constant high V<sub>PP</sub> and use the register commands for all operations, or to switch the V<sub>PP</sub> from low to high only when needing to erase or program the memory. All command register access is inhibited when V<sub>CC</sub> falls below the Erase/Write Lockout Voltage (V<sub>LKO</sub>) of 2.5V.

If the device is deselected during Erasure, Programming or Verification it will draw active supply currents until the operations are terminated.

The device is protected against stress caused by long erase or program times. If the end of Erase or Programming operations are not terminated by a Verify cycle within a maximum time permitted, an internal stop timer automatically stops the operation. The device remains in an inactive state, ready to start a Verify or Reset Mode operation.

#### Table 8. DC Characteristics

| Symbol                          | Parameter                                  | Test Condition                           | Min                  | Мах                                                                                                                                                                           | Unit |

|---------------------------------|--------------------------------------------|------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| ILI                             | Input Leakage Current                      | $0V \leq V_{IN} \leq V_{CC}$             |                      | ±1                                                                                                                                                                            | μA   |

| I <sub>LO</sub>                 | Output Leakage Current                     | $0V \le V_{OUT} \le V_{CC}$              |                      | ±10                                                                                                                                                                           | μA   |

| I <sub>CC</sub>                 | Supply Current (Read)                      | $\overline{E} = V_{IL}, f = 6MHz$        |                      | 30                                                                                                                                                                            | mA   |

| lee.                            | Supply Current (Standby) TTL               | E = V <sub>IH</sub>                      |                      | 1                                                                                                                                                                             | mA   |

| I <sub>CC1</sub>                | Supply Current (Standby) CMOS              | $\overline{E} = V_{CC} \pm 0.2V$         |                      | 50                                                                                                                                                                            | μA   |

| I <sub>CC2</sub> <sup>(1)</sup> | Supply Current (Programming)               | During Programming                       |                      | 10                                                                                                                                                                            | mA   |

| I <sub>CC3</sub> <sup>(1)</sup> | Supply Current (Program Verify)            | During Verify                            |                      | 15                                                                                                                                                                            | mA   |

| I <sub>CC4</sub> <sup>(1)</sup> | Supply Current (Erase)                     | During Erasure                           |                      | 15                                                                                                                                                                            | mA   |

| I <sub>CC5</sub> <sup>(1)</sup> | Supply Current (Erase Verify)              | During Erase Verify                      |                      | 15                                                                                                                                                                            | mA   |

| I <sub>LPP</sub>                | Program Leakage Current                    | $V_{PP} \leq V_{CC}$                     |                      | ±10                                                                                                                                                                           | μA   |

| laa                             | Program Current (Read or                   | $V_{PP} > V_{CC}$                        | 120                  |                                                                                                                                                                               | μΑ   |

| IPP                             | Standby)                                   | $V_{PP} \leq V_{CC}$                     |                      | ±10                                                                                                                                                                           | μA   |

| I <sub>PP1</sub> <sup>(1)</sup> | Program Current (Programming)              | $V_{PP} = V_{PPH}$ , During Programming  |                      | 30                                                                                                                                                                            | mA   |

| I <sub>PP2</sub> <sup>(1)</sup> | Program Current (Program<br>Verify)        | $V_{PP} = V_{PPH}$ , During Verify       |                      | 5                                                                                                                                                                             | mA   |

| I <sub>PP3</sub> <sup>(1)</sup> | Program Current (Erase)                    | $V_{PP} = V_{PPH}$ , During Erase        |                      | 30                                                                                                                                                                            | mA   |

| I <sub>PP4</sub> <sup>(1)</sup> | Program Current (Erase Verify)             | $V_{PP} = V_{PPH}$ , During Erase Verify |                      | 5                                                                                                                                                                             | mA   |

| V <sub>IL</sub>                 | Input Low Voltage                          |                                          | -0.5                 | 0.8                                                                                                                                                                           | V    |

| VIH                             | Input High Voltage TTL                     |                                          | 2                    | V <sub>CC</sub> + 0.5                                                                                                                                                         | V    |

| vп                              | Input High Voltage CMOS                    |                                          | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> + 0.5                                                                                                                                                         | V    |

| V <sub>OL</sub>                 | Output Low Voltage                         | I <sub>OL</sub> = 5.8mA (grade 1)        |                      | $\begin{array}{c} \pm 1 \\ \pm 10 \\ 30 \\ 1 \\ 50 \\ 10 \\ 15 \\ 15 \\ 15 \\ \pm 10 \\ 120 \\ \pm 10 \\ 30 \\ 5 \\ 30 \\ 5 \\ 30 \\ 5 \\ 0.8 \\ V_{CC} + 0.5 \\ \end{array}$ | V    |

| VOL                             | Oulput Low Voltage                         | l <sub>OL</sub> = 2.1mA (grade 6)        |                      |                                                                                                                                                                               | V    |

|                                 | Output High Voltage CMOS                   | I <sub>OH</sub> = −100μA                 | 4.1                  | $     1     50     10     15     15     15     15     \pm 10     120     \pm 10 30 5 30 5 30 5 0.8 V_{CC} + 0.5 0.45 0.45 0.45 0.45 0.45 0.45 0.45 12.6 13$                   | V    |

| V <sub>OH</sub>                 | Culput high voltage CiviCO                 | I <sub>OH</sub> = -2.5mA                 | 0.85 V <sub>CC</sub> |                                                                                                                                                                               | V    |

|                                 | Output High Voltage TTL                    | I <sub>OH</sub> = -2.5mA                 | 2.4                  |                                                                                                                                                                               | V    |

| V <sub>PPL</sub>                | Program Voltage (Read<br>Operations)       |                                          | 0                    | 6.5                                                                                                                                                                           | V    |

| V <sub>PPH</sub>                | Program Voltage (Read/Write<br>Operations) |                                          | 11.4                 | 12.6                                                                                                                                                                          | V    |

| V <sub>ID</sub>                 | A9 Voltage (Electronic Signature)          |                                          | 11.5                 | 13                                                                                                                                                                            | V    |

| I <sub>ID</sub> <sup>(1)</sup>  | A9 Current (Electronic Signature)          | A9 = V <sub>ID</sub>                     |                      | 200                                                                                                                                                                           | μΑ   |

| V <sub>LKO</sub>                | Supply Voltage, Erase/Program<br>Lock-out  |                                          | 2.5                  |                                                                                                                                                                               | V    |

57

Note: 1. Not 100% tested. Characterisation Data available.

#### Table 9A. Read Only Mode AC Characteristics

$(T_A = 0 \text{ to } 70 \text{ }^{\circ}\text{C}, -40 \text{ to } 85 \text{ }^{\circ}\text{C} \text{ or } -40 \text{ to } 125 \text{ }^{\circ}\text{C}; 0V \le V_{PP} \le 6.5V)$

|                                  |                  |                                            |                                                  | M28F101               |       |                    |       |                       |       |      |

|----------------------------------|------------------|--------------------------------------------|--------------------------------------------------|-----------------------|-------|--------------------|-------|-----------------------|-------|------|

|                                  |                  |                                            |                                                  | -70                   |       | -90                |       | -100                  |       | ]    |

| Symbol                           | Alt              | Parameter                                  | Test Condition                                   | V <sub>cc</sub> =5    | öV±5% | V <sub>CC</sub> =5 | V±10% | V <sub>CC</sub> =5    | V±10% | Unit |

|                                  |                  |                                            |                                                  | Standard<br>Interface |       |                    |       | Standard<br>Interface |       |      |

|                                  |                  |                                            |                                                  | Min                   | Max   | Min                | Max   | Min                   | Max   |      |

| t <sub>WHGL</sub>                |                  | Write Enable High to<br>Output Enable Low  |                                                  | 6                     |       | 6                  |       | 6                     |       | μs   |

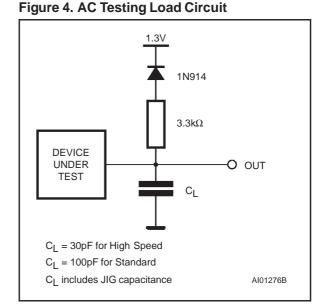

| t <sub>AVAV</sub>                | t <sub>RC</sub>  | Read Cycle Time                            | $\overline{E} = V_{IL}, \ \overline{G} = V_{IL}$ | 70                    |       | 90                 |       | 100                   |       | ns   |

| t <sub>AVQV</sub>                | t <sub>ACC</sub> | Address Valid to<br>Output Valid           | $\overline{E} = V_{IL},  \overline{G} = V_{IL}$  |                       | 70    |                    | 90    |                       | 100   | ns   |

| t <sub>ELQX</sub> <sup>(1)</sup> | t <sub>LZ</sub>  | Chip Enable Low to<br>Output Transition    | $\overline{G} = V_{IL}$                          | 0                     |       | 0                  |       | 0                     |       | ns   |

| t <sub>ELQV</sub>                | t <sub>CE</sub>  | Chip Enable Low to<br>Output Valid         | $\overline{G} = V_{IL}$                          |                       | 70    |                    | 90    |                       | 100   | ns   |

| $t_{GLQX}$ <sup>(1)</sup>        | t <sub>OLZ</sub> | Output Enable Low to<br>Output Transition  | $\overline{E} = V_{IL}$                          | 0                     |       | 0                  |       | 0                     |       | ns   |

| t <sub>GLQV</sub>                | t <sub>OE</sub>  | Output Enable Low to<br>Output Valid       | $\overline{E} = V_{IL}$                          |                       | 40    |                    | 40    |                       | 45    | ns   |

| t <sub>EHQZ</sub> <sup>(1)</sup> |                  | Chip Enable High to<br>Output Hi-Z         | $\overline{G} = V_{IL}$                          | 0                     | 30    | 0                  | 45    | 0                     | 45    | ns   |

| t <sub>GHQZ</sub> <sup>(1)</sup> | t <sub>DF</sub>  | Output Enable High to<br>Output Hi-Z       | $\overline{E} = V_{IL}$                          | 0                     | 30    | 0                  | 30    | 0                     | 30    | ns   |

| taxqx                            | tон              | Address Transition to<br>Output Transition | $\overline{E} = V_{IL}, \overline{G} = V_{IL}$   | 0                     |       | 0                  |       | 0                     |       | ns   |

Note: 1. Sampled only, not 100% tested

**Read Mode.** The Read Mode is the default at power up or may be set-up by writing 00h to the command register. Subsequent read operations outputdata from the memory. The memory remains in the Read Mode until a new command is written to the command register.

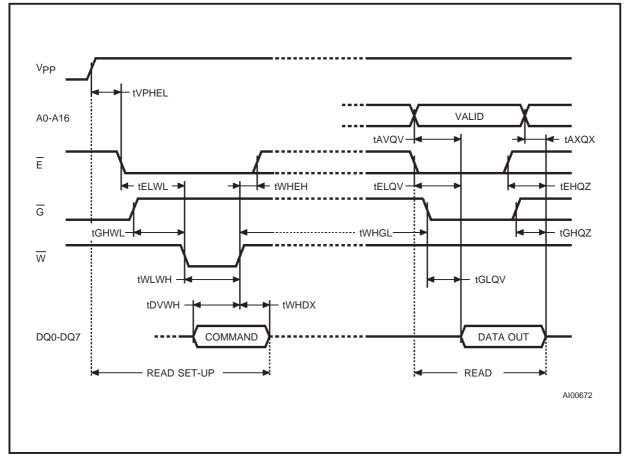

**Electronic Signature Mode.** In order to select the correct erase and programming algorithms for onboard programming, the manufacturer and device

codes may be read directly. It is not neccessary to apply a high voltage to A9 when using the command register. The Electronic Signature Mode is set-up by writing 90h to the command register. The following read cycles, with address inputs 00000h or 00001h, output the manufacturer or device type codes. The command is terminated by writing another valid command to the command register (for example Reset).

#### Table 9B. Read Only Mode AC Characteristics

((T<sub>A</sub> = 0 to 70 °C, -40 to 85 °C or -40 to 125 °C;  $0V \le V_{PP} \le 6.5V$ )

|                                  |                  |                                            |                                                 |                    |              | M28                | F101         |                    |               |      |

|----------------------------------|------------------|--------------------------------------------|-------------------------------------------------|--------------------|--------------|--------------------|--------------|--------------------|---------------|------|

|                                  |                  |                                            |                                                 | -12                | 20           | -1                 | 50           | -2                 | 00            |      |

| Symbol                           | Alt              | Parameter                                  | Test Condition                                  | V <sub>CC</sub> =5 | V±10%        | V <sub>CC</sub> =5 | V±10%        | V <sub>CC</sub> =5 | V±10%         | Unit |

|                                  |                  |                                            |                                                 |                    | dard<br>face | Stan<br>Inter      | dard<br>face |                    | dard<br>rface |      |

|                                  |                  |                                            |                                                 | Min                | Мах          | Min                | Мах          | Min                | Мах           |      |

| t <sub>WHGL</sub>                |                  | Write Enable High to<br>Output Enable Low  |                                                 | 6                  |              | 6                  |              | 6                  |               | μs   |

| t <sub>A VAV</sub>               | t <sub>RC</sub>  | Read Cycle Time                            | $\overline{E}=V_{IL},\overline{G}=V_{IL}$       | 120                |              | 150                |              | 200                |               | ns   |

| t <sub>AVQV</sub>                | t <sub>ACC</sub> | Address Valid to<br>Output Valid           | $\overline{E} = V_{IL},  \overline{G} = V_{IL}$ |                    | 120          |                    | 150          |                    | 200           | ns   |

| t <sub>ELQX</sub> <sup>(1)</sup> | t∟z              | Chip Enable Low to<br>Output Transition    | $\overline{G} = V_{IL}$                         | 0                  |              | 0                  |              | 0                  |               | ns   |

| t <sub>ELQV</sub>                | t <sub>CE</sub>  | Chip Enable Low to<br>Output Valid         | $\overline{G} = V_{IL}$                         |                    | 120          |                    | 150          |                    | 200           | ns   |

| t <sub>GLQX</sub> <sup>(1)</sup> | t <sub>OLZ</sub> | Output Enable Low to<br>Output Transition  | $\overline{E} = V_{IL}$                         | 0                  |              | 0                  |              | 0                  |               | ns   |

| t <sub>GLQV</sub>                | t <sub>OE</sub>  | Output Enable Low to<br>Output Valid       | $\overline{E} = V_{IL}$                         |                    | 50           |                    | 55           |                    | 60            | ns   |

| t <sub>EHQZ</sub> <sup>(1)</sup> |                  | Chip Enable High to<br>Output Hi-Z         | $\overline{G} = V_{IL}$                         | 0                  | 55           | 0                  | 55           | 0                  | 60            | ns   |

| t <sub>GHQZ</sub> <sup>(1)</sup> | t <sub>DF</sub>  | Output Enable High to<br>Output Hi-Z       | $\overline{E} = V_{IL}$                         | 0                  | 30           | 0                  | 35           | 0                  | 40            | ns   |

| t <sub>AXQX</sub>                | tон              | Address Transition to<br>Output Transition | $\overline{E} = V_{IL}, \overline{G} = V_{IL}$  | 0                  |              | 0                  |              | 0                  |               | ns   |

Note: 1. Sampled only, not 100% tested

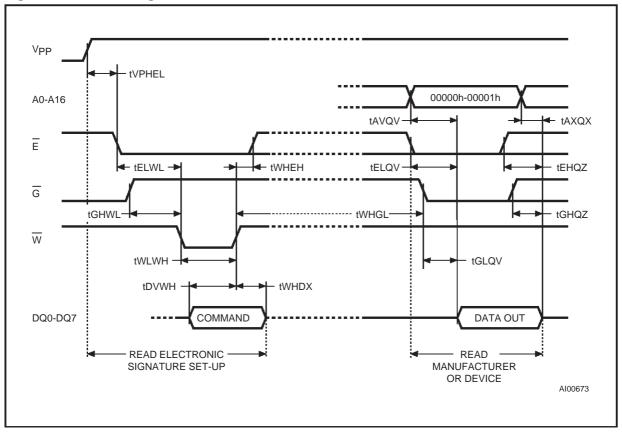

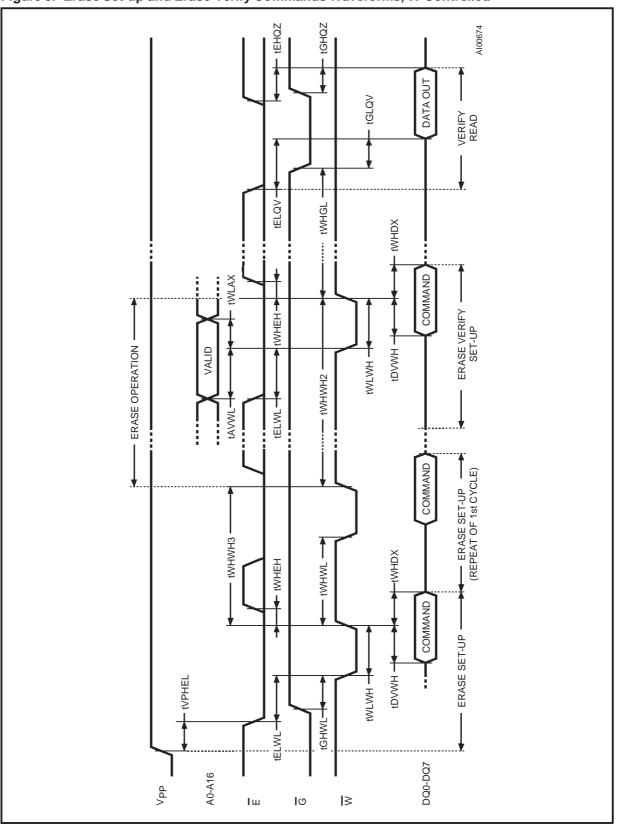

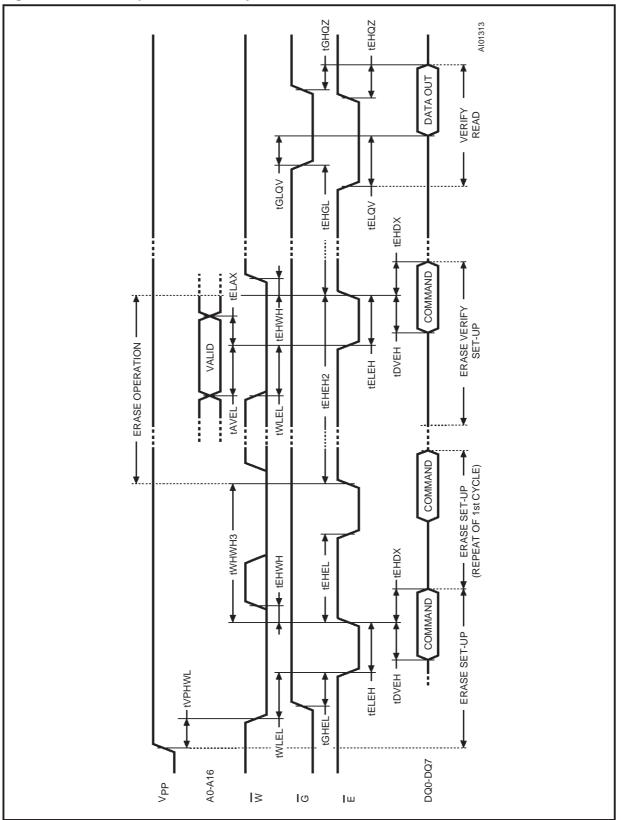

**Erase and Erase Verify Modes.** The memory is erased by first Programming all bytes to 00h, the Erase command then erases them to FFh. The Erase Verify command is then used to read the memory byte-by-byte for a content of FFh. The Erase Mode is set-up by writing 20h to the command register. The write cycle is then repeated to start the erase operation. Erasure starts on the rising edge of  $\overline{W}$  during this second cycle. Erase is followed by an Erase Verify which reads an addressed byte. Erase Verify Mode is set-up by writing A0h to the command register and at the same time supplying the address of the byte to be verified. The rising edge of  $\overline{W}$  during the set-up of the first Erase Verify Mode stops the Erase operation. The following read cycle is made with an internally generated margin voltage applied; reading FFh indicates that all bits of the addressed byte are fully erased. The whole contents of the memory are verified by repeating the Erase Verify Operation, first writing the set-up code A0h with the address of the byte to be verified and then reading the byte contents in a second read cycle.

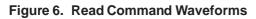

Figure 5. Read Mode AC Waveforms

Figure 7. Electronic Signature Command Waveforms

#### READ/WRITE MODES (cont'd)

As the Erase algorithm flow chart shows, when the data read during Erase Verify is not FFh, another Erase operation is performed and verification continues from the address of the last verified byte. The command is terminated by writing another valid command to the command register (for example Program or Reset).

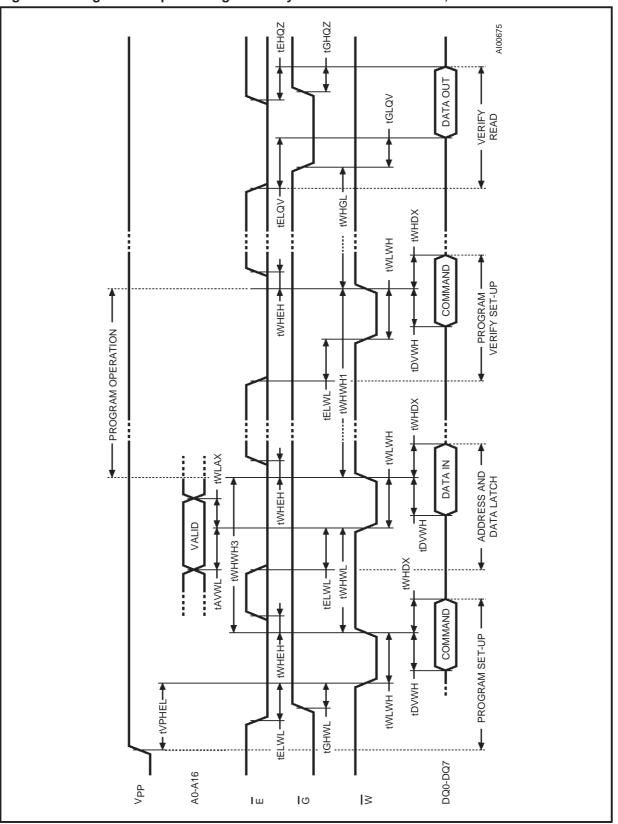

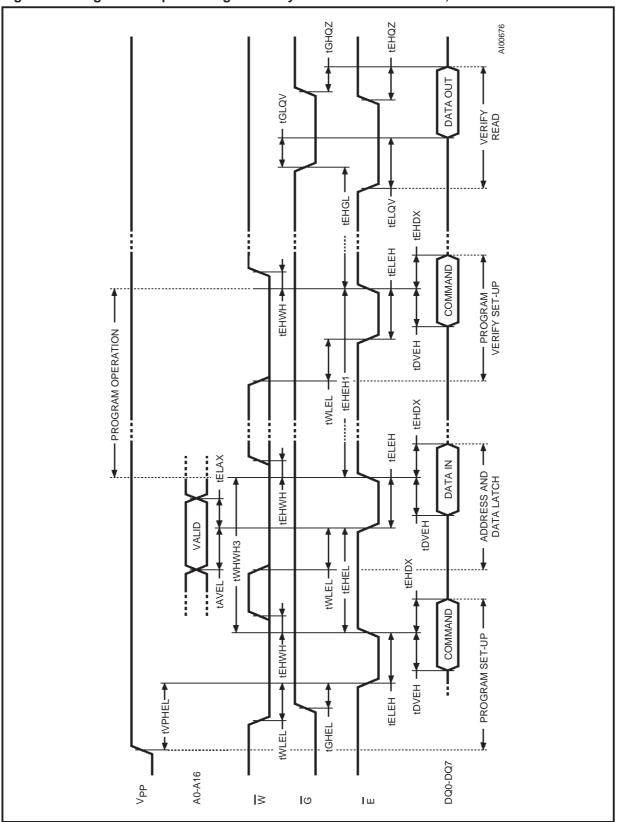

**Program and Program Verify Modes.** The ProgramMode is set-up by writing 40h to the command register. This is followed by a second write cycle which latches the address and data of the byte to be programmed. The rising edge of W during this secind cycle starts the programming operation. Programming is followed by a Program Verify of the data written. Program Verify Mode is set-up by writing C0h to the command register. The rising edge of W during the set-up of the Program Verify Mode stops the Programming operation. The following read cycle, of the address already latched during programming, is made with an internally generated margin voltage applied, reading valid data indicates that all bits have been programmed.

**Reset Mode.** This command is used to safely abort Erase or Program Modes. The Reset Mode is set-up and performed by writing FFh two times to the command register. The command should be followed by writing a valid command to the the command register (for example Read).

# Table 10A. Read/Write Mode AC Characteristics, $\overline{W}$ and $\overline{E}$ Controlled (T<sub>A</sub> = 0 to 70 °C, -40 to 85 °C or -40 to 125 °C)

|                                  |                  |                                                        |                       |            | M28                   | F101  |                       |       |      |

|----------------------------------|------------------|--------------------------------------------------------|-----------------------|------------|-----------------------|-------|-----------------------|-------|------|

|                                  |                  |                                                        | -7                    | <b>'</b> 0 | -9                    | 90    | -1                    | 00    | 1    |

| Symbol                           | Alt              | Parameter                                              | V <sub>cc</sub> =5    | V±5%       | V <sub>CC</sub> =5    | V±10% | V <sub>CC</sub> =5    | V±10% | Unit |

|                                  |                  |                                                        | Standard<br>Interface |            | Standard<br>Interface |       | Standard<br>Interface |       |      |

|                                  |                  |                                                        | Min                   | Max        | Min                   | Max   | Min                   | Max   |      |

| t <sub>VPHEL</sub>               |                  | V <sub>PP</sub> High to Chip Enable Low                | 1                     |            | 1                     |       | 1                     |       | μs   |

| t <sub>VPHWL</sub>               |                  | V <sub>PP</sub> High to Write Enable Low               | 1                     |            | 1                     |       | 1                     |       | μs   |

| t <sub>WHWH3</sub>               | t <sub>WC</sub>  | Write Cycle Time                                       | 70                    |            | 90                    |       | 100                   |       | ns   |

| t <sub>AVWL</sub>                | t <sub>AS</sub>  | Address Valid to Write Enable Low                      | 0                     |            | 0                     |       | 0                     |       | ns   |

| tAVEL                            |                  | Address Valid to Chip Enable Low                       | 0                     |            | 0                     |       | 0                     |       | ns   |

| t <sub>WLAX</sub>                | t <sub>AH</sub>  | Write Enable Low to Address Transition                 | 40                    |            | 40                    |       | 40                    |       | ns   |

| t <sub>ELAX</sub>                |                  | Chip Enable Low to Address Transition                  | 50                    |            | 60                    |       | 60                    |       | ns   |

| t <sub>ELWL</sub>                | t <sub>CS</sub>  | Chip Enable Low to Write Enable Low                    | 10                    |            | 15                    |       | 15                    |       | ns   |

| t <sub>WLEL</sub>                |                  | Write Enable Low to Chip Enable Low                    | 0                     |            | 0                     |       | 0                     |       | ns   |

| t <sub>GHWL</sub>                |                  | Output Enable High to Write Enable Low                 | 0                     |            | 0                     |       | 0                     |       | μs   |

| t <sub>GHEL</sub>                |                  | Output Enable High to Chip Enable Low                  | 0                     |            | 0                     |       | 0                     |       | μs   |

| t <sub>DVWH</sub>                | t <sub>DS</sub>  | Input Valid to Write Enable High                       | 30                    |            | 40                    |       | 40                    |       | ns   |

| <b>t</b> DVEH                    |                  | Input Valid to Chip Enable High                        | 30                    |            | 35                    |       | 40                    |       | ns   |

| t <sub>WLWH</sub>                | t <sub>WP</sub>  | Write Enable Low to Write Enable High<br>(Write Pulse) | 35                    |            | 40                    |       | 40                    |       | ns   |

| t <sub>ELEH</sub>                |                  | Chip Enable Low to Chip Enable High<br>(Write Pulse)   | 35                    |            | 45                    |       | 45                    |       | ns   |

| t <sub>WHDX</sub>                | t <sub>DH</sub>  | Write Enable High to Input Transition                  | 10                    |            | 10                    |       | 10                    |       | ns   |

| t <sub>EHDX</sub>                |                  | Chip Enable High to Input Transition                   | 10                    |            | 10                    |       | 10                    |       | ns   |

| t <sub>WHWH1</sub>               |                  | Duration of Program Operation                          | 9.5                   |            | 9.5                   |       | 9.5                   |       | μs   |

| t <sub>EHEH1</sub>               |                  | Duration of Program Operation                          | 9.5                   |            | 9.5                   |       | 9.5                   |       | μs   |

| t <sub>WHWH2</sub>               |                  | Duration of Erase Operation                            | 9.5                   |            | 9.5                   |       | 9.5                   |       | ms   |

| t <sub>WHEH</sub>                | t <sub>CH</sub>  | Write Enable High to Chip Enable High                  | 0                     |            | 0                     |       | 0                     |       | ns   |

| t <sub>EHWH</sub>                |                  | Chip Enable High to Write Enable High                  | 0                     |            | 0                     |       | 0                     |       | ns   |

| twhwL                            | t <sub>WPH</sub> | Write Enable High to Write Enable Low                  | 20                    |            | 20                    |       | 20                    |       | ns   |

| t <sub>EHEL</sub>                |                  | Chip Enable High to Chip Enable Low                    | 20                    |            | 20                    |       | 20                    |       | ns   |

| t <sub>WHGL</sub>                |                  | Write Enable High to Output Enable Low                 | 6                     |            | 6                     |       | 6                     |       | μs   |

| t <sub>EHGL</sub>                |                  | Chip Enable High to Output Enable Low                  | 6                     |            | 6                     |       | 6                     |       | μs   |

| t <sub>AVQV</sub>                | t <sub>ACC</sub> | Addess Valid to data Output                            |                       | 70         |                       | 90    |                       | 100   | ns   |

| t <sub>ELQX</sub> <sup>(1)</sup> | t <sub>LZ</sub>  | Chip Enable Low to Output Transition                   | 0                     |            | 0                     |       | 0                     |       | ns   |

| t <sub>ELQV</sub>                | t <sub>CE</sub>  | Chip Enable Low to Output Valid                        |                       | 70         |                       | 90    |                       | 100   | ns   |

| t <sub>GLQX</sub> <sup>(1)</sup> | t <sub>OLZ</sub> | Output Enable Low to Output Transition                 | 0                     |            | 0                     |       | 0                     |       | ns   |

| <b>t</b> GLQV                    | toe              | Output Enable Low to Output Valid                      |                       | 40         |                       | 40    |                       | 45    | ns   |

| t <sub>EHQZ</sub> <sup>(1)</sup> |                  | Chip Enable High to Output Hi-Z                        |                       | 30         |                       | 40    |                       | 40    | ns   |

| t <sub>GHQZ</sub> (1)            | t <sub>DF</sub>  | Output Enable High to Output Hi-Z                      |                       | 30         |                       | 30    |                       | 30    | ns   |

| t <sub>AXQX</sub>                | t <sub>OH</sub>  | Address Transition to Output Transition                | 0                     |            | 0                     |       | 0                     |       | ns   |

Note: 1. Sampled only, not 100% tested.

# Table 10B. Read/Write Mode AC Characteristics, $\overline{W}$ and $\overline{E}$ Controlled (T\_A = 0 to 70 °C, -40 to 85 °C or -40 to 125 °C)

|                                  |                  |                                                        | M28F101               |       |                       |       |                       |       |      |

|----------------------------------|------------------|--------------------------------------------------------|-----------------------|-------|-----------------------|-------|-----------------------|-------|------|

|                                  |                  |                                                        | -1                    | 20    | -1                    | 50    | -2                    | 00    | 1    |

| Symbol                           | Alt              | Parameter                                              | V <sub>CC</sub> =5    | V±10% | V <sub>CC</sub> =5    | V±10% | V <sub>CC</sub> =5    | V±10% | Unit |

|                                  |                  |                                                        | Standard<br>Interface |       | Standard<br>Interface |       | Standard<br>Interface |       |      |

|                                  |                  |                                                        | Min                   | Max   | Min                   | Max   | Min                   | Max   |      |

| t <sub>VPHEL</sub>               |                  | V <sub>PP</sub> High to Chip Enable Low                | 1                     |       | 1                     |       | 1                     |       | μs   |

| t <sub>VPHWL</sub>               |                  | V <sub>PP</sub> High to Write Enable Low               | 1                     |       | 1                     |       | 1                     |       | μs   |

| t <sub>WHWH3</sub>               | t <sub>WC</sub>  | Write Cycle Time                                       | 120                   |       | 150                   |       | 200                   |       | ns   |

| t <sub>AVWL</sub>                | t <sub>AS</sub>  | Address Valid to Write Enable Low                      | 0                     |       | 0                     |       | 0                     |       | ns   |

| t <sub>AVEL</sub>                |                  | Address Valid to Chip Enable Low                       | 0                     |       | 0                     |       | 0                     |       | ns   |

| t <sub>WLAX</sub>                | t <sub>AH</sub>  | Write Enable Low to Address Transition                 | 60                    |       | 60                    |       | 75                    |       | ns   |

| t <sub>ELAX</sub>                |                  | Chip Enable Low to Address Transition                  | 80                    |       | 80                    |       | 80                    |       | ns   |

| t <sub>ELWL</sub>                | t <sub>CS</sub>  | Chip Enable Low to Write Enable Low                    | 20                    |       | 20                    |       | 20                    |       | ns   |

| t <sub>WLEL</sub>                |                  | Write Enable Low to Chip Enable Low                    | 0                     |       | 0                     |       | 0                     |       | ns   |

| t <sub>GHWL</sub>                |                  | Output Enable High to Write Enable Low                 | 0                     |       | 0                     |       | 0                     |       | μs   |

| t <sub>GHEL</sub>                |                  | Output Enable High to Chip Enable Low                  | 0                     |       | 0                     |       | 0                     |       | μs   |

| t <sub>DVWH</sub>                | t <sub>DS</sub>  | Input Valid to Write Enable High                       | 50                    |       | 50                    |       | 50                    |       | ns   |

| t <sub>DVEH</sub>                |                  | Input Valid to Chip Enable High                        | 50                    |       | 50                    |       | 50                    |       | ns   |

| t <sub>WLWH</sub>                | t <sub>WP</sub>  | Write Enable Low to Write Enable High<br>(Write Pulse) | 60                    |       | 60                    |       | 60                    |       | ns   |

| t <sub>ELEH</sub>                |                  | Chip Enable Low to Chip Enable High<br>(Write Pulse)   | 70                    |       | 70                    |       | 70                    |       | ns   |

| t <sub>WHDX</sub>                | t <sub>DH</sub>  | Write Enable High to Input Transition                  | 10                    |       | 10                    |       | 10                    |       | ns   |

| t <sub>EHDX</sub>                |                  | Chip Enable High to Input Transition                   | 10                    |       | 10                    |       | 10                    |       | ns   |

| t <sub>WHWH1</sub>               |                  | Duration of Program Operation                          | 9.5                   |       | 9.5                   |       | 9.5                   |       | μs   |

| t <sub>EHEH1</sub>               |                  | Duration of Program Operation                          | 9.5                   |       | 9.5                   |       | 9.5                   |       | μs   |

| t <sub>WHWH2</sub>               |                  | Duration of Erase Operation                            | 9.5                   |       | 9.5                   |       | 9.5                   |       | ms   |

| t <sub>WHEH</sub>                | t <sub>CH</sub>  | Write Enable High to Chip Enable High                  | 0                     |       | 0                     |       | 0                     |       | ns   |

| t <sub>EHWH</sub>                |                  | Chip Enable High to Write Enable High                  | 0                     |       | 0                     |       | 0                     |       | ns   |

| t <sub>WHWL</sub>                | twph             | Write Enable High to Write Enable Low                  | 20                    |       | 20                    |       | 20                    |       | ns   |

| t <sub>EHEL</sub>                |                  | Chip Enable High to Chip Enable Low                    | 20                    |       | 20                    |       | 20                    |       | ns   |

| t <sub>WHGL</sub>                |                  | Write Enable High to Output Enable<br>Low              | 6                     |       | 6                     |       | 6                     |       | μs   |

| t <sub>EHGL</sub>                |                  | Chip Enable High to Output Enable Low                  | 6                     |       | 6                     |       | 6                     |       | μs   |

| t <sub>AVQV</sub>                | t <sub>ACC</sub> | Addess Valid to data Output                            |                       | 120   |                       | 150   |                       | 200   | ns   |

| t <sub>ELQX</sub> <sup>(1)</sup> | t <sub>LZ</sub>  | Chip Enable Low to Output Transition                   | 0                     |       | 0                     |       | 0                     |       | ns   |

| t <sub>ELQV</sub>                | t <sub>CE</sub>  | Chip Enable Low to Output Valid                        |                       | 120   |                       | 150   |                       | 200   | ns   |

| t <sub>GLQX</sub> <sup>(1)</sup> | t <sub>OLZ</sub> | Output Enable Low to Output Transition                 | 0                     |       | 0                     |       | 0                     |       | ns   |

| <b>t</b> GLQV                    | toe              | Output Enable Low to Output Valid                      |                       | 50    |                       | 55    |                       | 60    | ns   |

| t <sub>EHQZ</sub> <sup>(1)</sup> |                  | Chip Enable High to Output Hi-Z                        |                       | 50    |                       | 55    |                       | 60    | ns   |

| t <sub>GHQZ</sub> <sup>(1)</sup> | t <sub>DF</sub>  | Output Enable High to Output Hi-Z                      |                       | 30    |                       | 35    |                       | 40    | ns   |

| t <sub>AXQX</sub>                | t <sub>OH</sub>  | Address Transition to Output Transition                | 0                     |       | 0                     |       | 0                     |       | ns   |

Note: 1. Sampled only, not 100% tested.

Figure 8. Erase Set-up and Erase Verify Commands Waveforms, W Controlled

Figure 9. Erase Set-up and Erase Verify Commands Waveforms, E Controlled

Figure 10. Program Set-up and Program Verify Commands Waveforms, W Controlled

Figure 11. Program Set-up and Program Verify Commands Waveforms, E Controlled

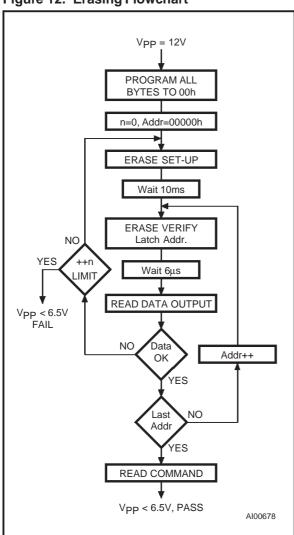

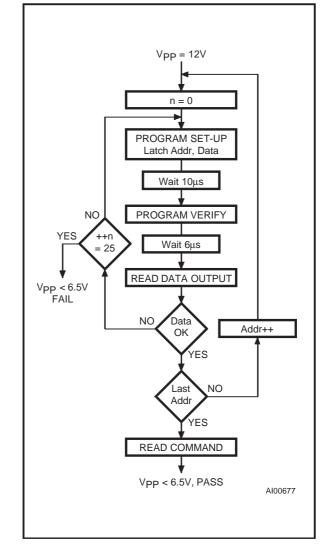

Figure 12. Erasing Flowchart

Limit: 1000 at grade 1; 6000 at grades 3 & 6.

#### PRESTO F ERASE ALGORITHM

The PRESTO F Erase Algorithm guarantees that the device will be erased in a reliable way. The algorithm first programms all bytes to 00h in order to ensure uniform erasure. The programming follows the PRESTO F Programming Algorithm. Erase is set-up by writing 20h to the command register, the erasure is started by repeating this write cycle. Erase Verify is set-up by writing AOh to the command register together with the address of the byte to be verified. The subsequent read cycle reads the data which is compared to FFh. Erase Verify begins at address 0000h and continues to the last address or until the comparison of the data to 0FFh fails. If this occurs, the address of the last byte checked is stored and a new Erase operation performed. Erase Verify then continues from the address of the stored location.

Figure 13. Programming Flowchart

#### PRESTO F PROGRAM ALGORITHM

The PRESTO F Programming Algorithm applies a series of 10µs programming pulses to a byte until a correct verify occurs. Up to 25 programming operations are allowed for one byte. Program is set-up by writing 40h to the command register, the programming is started after the next write cycle which also latches the address and data to be programmed. Program Verify is set-up by writing C0h to the command register, followed by a read cycle and a compare of the data read to the data expected. During Program and Program Verify operations a MARGIN MODE circuit is activated to guarantee that the cell is programmed with a safety margin.

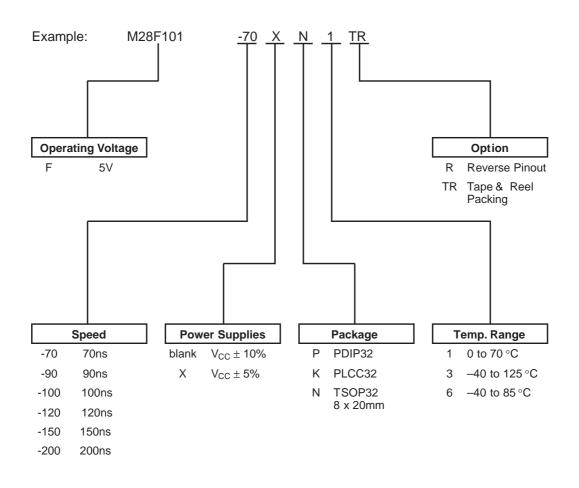

#### **ORDERING INFORMATION SCHEME**

Devices are shipped from the factory with the memory content erased (to FFh).

For a list of available options (Speed, Package, etc...) or for further information on any aspect of this device, please contact the STMicroelectronics Sales Office nearest to you.

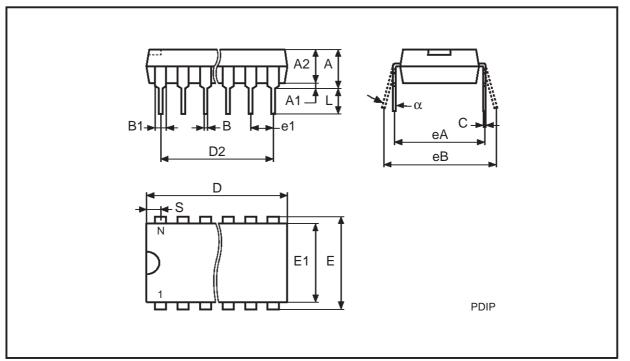

| Symb |       | mm    |       | inches |       |       |  |  |

|------|-------|-------|-------|--------|-------|-------|--|--|

|      | Тур   | Min   | Max   | Тур    | Min   | Мах   |  |  |

| А    |       | _     | 5.08  |        | _     | 0.200 |  |  |

| A1   |       | 0.38  | -     |        | 0.015 | _     |  |  |

| A2   |       | 3.56  | 4.06  |        | 0.140 | 0.160 |  |  |

| В    |       | 0.38  | 0.51  |        | 0.015 | 0.020 |  |  |

| B1   | 1.52  | -     | -     | 0.060  | -     | _     |  |  |

| С    |       | 0.20  | 0.30  |        | 0.008 | 0.012 |  |  |

| D    |       | 41.78 | 42.04 |        | 1.645 | 1.655 |  |  |

| D2   | 38.10 | -     | -     | 1.500  | _     | _     |  |  |

| E    | 15.24 | -     | -     | 0.600  | -     | _     |  |  |

| E1   |       | 13.59 | 13.84 |        | 0.535 | 0.545 |  |  |

| e1   | 2.54  | -     | -     | 0.100  | -     | -     |  |  |

| eA   | 15.24 | _     | _     | 0.600  | -     | _     |  |  |

| eB   |       | 15.24 | 17.78 |        | 0.600 | 0.700 |  |  |

| L    |       | 3.18  | 3.43  |        | 0.125 | 0.135 |  |  |

| S    |       | 1.78  | 2.03  |        | 0.070 | 0.080 |  |  |

| α    |       | 0°    | 10°   |        | 0°    | 10°   |  |  |

| N    |       | 32    | •     |        | 32    |       |  |  |

PDIP32 - 32 pin Plastic DIP, 600 mils width

Drawing is not to scale.

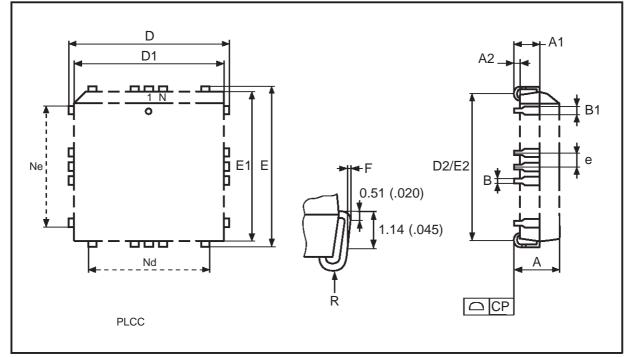

| Symb |      | mm    |       | inches |       |       |  |

|------|------|-------|-------|--------|-------|-------|--|

|      | Тур  | Min   | Max   | Тур    | Min   | Max   |  |

| А    |      | 2.54  | 3.56  |        | 0.100 | 0.140 |  |

| A1   |      | 1.52  | 2.41  |        | 0.060 | 0.095 |  |

| A2   |      | -     | 0.38  |        | _     | 0.015 |  |

| В    |      | 0.33  | 0.53  |        | 0.013 | 0.021 |  |

| B1   |      | 0.66  | 0.81  |        | 0.026 | 0.032 |  |

| D    |      | 12.32 | 12.57 |        | 0.485 | 0.495 |  |

| D1   |      | 11.35 | 11.56 |        | 0.447 | 0.455 |  |

| D2   |      | 9.91  | 10.92 |        | 0.390 | 0.430 |  |

| E    |      | 14.86 | 15.11 |        | 0.585 | 0.595 |  |

| E1   |      | 13.89 | 14.10 |        | 0.547 | 0.555 |  |

| E2   |      | 12.45 | 13.46 |        | 0.490 | 0.530 |  |

| е    | 1.27 | -     | -     | 0.050  | _     | _     |  |

| F    |      | 0.00  | 0.25  |        | 0.000 | 0.010 |  |

| R    | 0.89 | -     | _     | 0.035  | _     | _     |  |

| Ν    |      | 32    |       |        | 32    |       |  |

| Nd   | 7    |       |       | 7      |       |       |  |

| Ne   |      | 9     |       | 9      |       |       |  |

| СР   |      |       | 0.10  |        |       | 0.004 |  |

## PLCC32 - 32 lead Plastic Leaded Chip Carrier, rectangular

Drawing is not to scale.

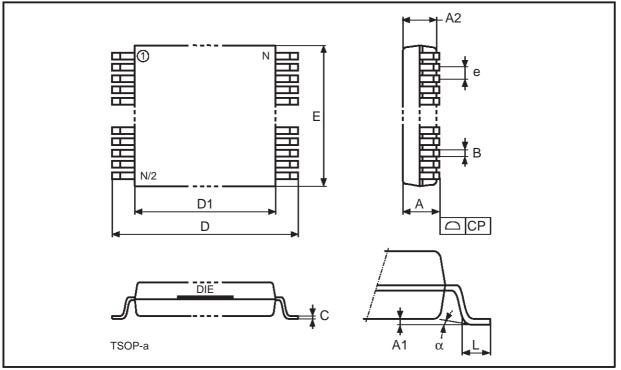

| Symb  |      | mm    |       |       | inches |       |

|-------|------|-------|-------|-------|--------|-------|

| Cynib | Тур  | Min   | Мах   | Тур   | Min    | Max   |

| А     |      |       | 1.20  |       |        | 0.047 |

| A1    |      | 0.05  | 0.15  |       | 0.002  | 0.007 |

| A2    |      | 0.95  | 1.05  |       | 0.037  | 0.041 |

| В     |      | 0.15  | 0.27  |       | 0.006  | 0.011 |

| С     |      | 0.10  | 0.21  |       | 0.004  | 0.008 |

| D     |      | 19.80 | 20.20 |       | 0.780  | 0.795 |

| D1    |      | 18.30 | 18.50 |       | 0.720  | 0.728 |

| E     |      | 7.90  | 8.10  |       | 0.311  | 0.319 |

| е     | 0.50 | -     | -     | 0.020 | -      | -     |

| L     |      | 0.50  | 0.70  |       | 0.020  | 0.028 |

| α     |      | 0°    | 5°    |       | 0°     | 5°    |

| Ν     |      | 32    |       |       | 32     |       |

| СР    |      |       | 0.10  |       |        | 0.004 |

## TSOP32 Normal Pinout - 32 lead Plastic Thin Small Outline, 8 x 20mm

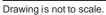

| TSOP32 | 2 Reverse I | Pinout - 32 | lead Plastic | Thin Small | Outline, 8 | x 20mm |  |  |

|--------|-------------|-------------|--------------|------------|------------|--------|--|--|

| Symb   | mm          |             |              | inches     |            |        |  |  |

| Cynno  | Тур         | Min         | Max          | Тур        | Min        | Max    |  |  |

| А      |             |             | 1.20         |            |            | 0.047  |  |  |

| A1     |             | 0.05        | 0.15         |            | 0.002      | 0.007  |  |  |

| A2     |             | 0.95        | 1.05         |            | 0.037      | 0.041  |  |  |

| В      |             | 0.15        | 0.27         |            | 0.006      | 0.011  |  |  |

| С      |             | 0.10        | 0.21         |            | 0.004      | 0.008  |  |  |

| D      |             | 19.80       | 20.20        |            | 0.780      | 0.795  |  |  |

| D1     |             | 18.30       | 18.50        |            | 0.720      | 0.728  |  |  |

| E      |             | 7.90        | 8.10         |            | 0.311      | 0.319  |  |  |

| е      | 0.50        | -           | -            | 0.020      | -          | -      |  |  |

| L      |             | 0.50        | 0.70         |            | 0.020      | 0.028  |  |  |

| α      |             | 0°          | 5°           |            | 0°         | 5°     |  |  |

| N      |             | 32          |              |            | 32         |        |  |  |

| СР     |             |             | 0.10         |            |            | 0.004  |  |  |

Drawing is not to scale.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 1998 STMicroelectronics - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands -Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.