#### Features

- EE Programmable 524,288 x 1- and 1,048,576 x 1-bit Serial Memories Designed to Store Configuration Programs for Field Programmable Gate Arrays (FPGAs)

- In-System Programmable via 2-wire Bus

- Simple Interface to SRAM FPGAs

- Compatible with Atmel AT6000, AT40K FPGAs, Altera FLEX<sup>®</sup> Devices, Lucent ORCA<sup>®</sup> FPGAs, Xilinx XC3000, XC4000, XC5200, SPARTAN<sup>®</sup> and Virtex<sup>®</sup> FPGAs

- Cascadable Read Back to Support Additional Configurations or Future Higher-density Arrays

- Low-power CMOS EEPROM Process

- Programmable Reset Polarity

- Available in PLCC Package (Pin-compatible Across Product Family)

- Emulation of Atmel's AT24CXXX Serial EEPROMs

- Available in 3.3V  $\pm$  10% LV and 5V  $\pm$  5% C Versions

- System-friendly READY Pin

- Low-power Standby Mode

#### Description

The AT17C512/010 and AT17LV512/010 (high-density AT17 Series) FPGA Configuration EEPROMs (Configurators) provide an easy-to-use, cost-effective configuration memory for Field Programmable Gate Arrays. The AT17 Series is packaged in the popular 20-pin PLCC. The AT17 Series family uses a simple serial-access procedure to configure one or more FPGA devices. The AT17 Series organization supplies enough memory to configure one or multiple smaller FPGAs. The user can select the polarity of the reset function by programming four EEPROM bytes. These devices also support a write protection mode and a system-friendly READY pin, which signifies a "good" power level to the FPGA and can be used to ensure reliable system power-up.

The AT17 Configurator Series can be programmed with industry-standard programmers, or Atmel's ATDH2200E Programming Kit.

# AMEL

FPGA Configuration EEPROM Memory

512K and 1M

# AT17C512 AT17LV512 AT17C010 AT17LV010

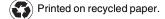

#### **Pin Configurations**

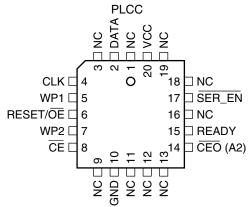

#### **Block Diagram**

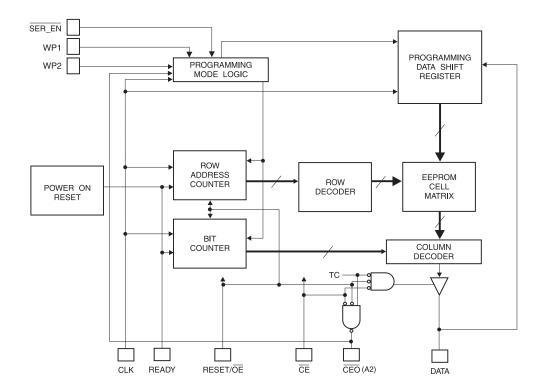

#### **FPGA Master Serial** The I/O and logic functions of the FPGA and their associated interconnections are established by a configuration program. The program is loaded either automatically Mode Summary upon power-up, or on command, depending on the state of the FPGA mode pins. In Master Mode, the FPGA automatically loads the configuration program from an external memory. The AT17 Serial Configuration EEPROM has been designed for compatibility with the Master Serial Mode. This document discusses the AT40K FPGA interface. For more details or AT6000 FPGA applications, please reference "AT40K Series Configuration" or "AT6000 Series Configuration" application notes. **Controlling the High-**Most connections between the FPGA device and the AT17 Serial Configuration EEPROM are simple and self-explanatory: density AT17 Series The DATA output of the AT17 Series Configurator drives DIN of the FPGA devices. Serial EEPROMs **During Configuration** The master FPGA CCLK output drives the CLK input of the AT17 Series Configurator. The $\overline{CEO}$ output of any AT17C/LV512/010 drives the $\overline{CE}$ input of the next AT17C/LV512/010 in a cascade chain of EEPROMs. SER EN must be connected to VCC, (except during ISP). The READY pin is available as an open-collector indicator of the device's reset status; it is driven Low while the device is in its power-on reset cycle and released (tri-stated) when the cycle is complete.

There are two different ways to use the inputs  $\overline{CE}$  and  $\overline{OE}$ .

#### **Condition 1**

The simplest connection is to have the FPGA  $\overline{\text{CON}}$  pin drive both  $\overline{\text{CE}}$  and  $\text{RESET}/\overline{\text{OE}}^{(1)}$  in parallel. Due to its simplicity, however, this method will fail if the FPGA receives an external reset condition during the configuration cycle. If a system reset is applied to the FPGA, it will abort the original configuration and then reset itself for a new configuration, as intended. Of course, the AT17 Series Configurator does not see the external reset signal and will not reset its internal address counters and, consequently, will remain out of sync with the FPGA for the remainder of the configuration cycle.

Note: 1. For this condition, the reset polarity of the EEPROM must be set active High.

Figure 1. Condition 2 Connection

reference the "Programming Specification for Atmel's FPGA Configuration EEPROMs" application note.

# **Programming Mode** The programming mode is entered by bringing SER\_EN Low. In this mode the chip can be programmed by the 2-wire serial bus. The programming is done at VCC supply only. Programming super voltages are generated inside the chip. See the "Programming Specification for Atmel's FPGA Configuration EEPROMs" application note for further information. The AT17C parts are read/write at 5V nominal. The AT17LV parts are read/write at 3.3V nominal.

**Standby Mode** The AT17C/LV512/010 Series Configurator enters a low-power standby mode whenever CE is asserted High. In this mode, the Configurator consumes less than 0.5 mA of current at 5V. The output remains in a high impedance state regardless of the state of the OE input.

#### **Pin Configurations**

| 20<br>PLCC<br>Pin | Name     | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                 | DATA     | I/O | Three-state DATA output for configuration. Open-collector bi-directional pin for programming.                                                                                                                                                                                                                                                                                                                       |

| 4                 | CLK      | I   | Clock input. Used to increment the internal address and bit counter for reading and programming.                                                                                                                                                                                                                                                                                                                    |

| 5                 | WP1      | I   | WRITE PROTECT (1). Used to protect portions of memory during programming. Disabled by default due to internal pull-down resistor. This input pin is not used during FPGA loading operations. See the "Programming Specification" application note for more details.                                                                                                                                                 |

| 6                 | RESET/OE | I   | RESET/Output Enable input (when SER_EN is High). A Low level on both the CE and RESET/OE inputs enables the data output driver. A High level on RESET/OE resets both the address and bit counters. The logic polarity of this input is programmable as either RESET/OE or RESET/OE. This document describes the pin as RESET/OE.                                                                                    |

| 7                 | WP2      | I   | WRITE PROTECT (2). Used to protect portions of memory during programming. Disabled by default due to internal pull-down resistor. This input pin is not used during FPGA loading operations. See the "Programming Specification" application note for more details.                                                                                                                                                 |

| 8                 | CE       | I   | Chip Enable input. Used for device selection. A Low level on both $\overline{CE}$ and $\overline{OE}$ enables the data output driver. A High level on $\overline{CE}$ disables both the address and bit counters and forces the device into a low-power standby mode. Note that this pin will <u>not</u> enable/disable the device in the 2-wire Serial Programming Mode (i.e., when $\overline{SER}_{EN}$ is Low). |

| 10                | GND      |     | Ground pin. A 0.2 µF decoupling capacitor between VCC and GND is recommended.                                                                                                                                                                                                                                                                                                                                       |

| 14                | CEO      | Ο   | Chip Enable Output. This signal is asserted Low on the clock cycle following the last bit read from the memory. It will stay Low as long as $\overline{CE}$ and $\overline{OE}$ are both Low. It will then follow $\overline{CE}$ until $\overline{OE}$ goes High. Thereafter, $\overline{CEO}$ will stay High until the entire EEPROM is read again.                                                               |

| 14                | A2       | I   | Device selection input, A2. This is used to enable (or select) the device during programming (i.e., when SER_EN is Low; see the "Programming Specification" application note for more details).                                                                                                                                                                                                                     |

| 15                | READY    | 0   | Open collector reset state indicator. Driven Low during power-up reset, released when power-up is complete. (Recommend a 4.7 k $\Omega$ pull-up on this pin if used).                                                                                                                                                                                                                                               |

| 17                | SER_EN   | Ι   | Serial enable must be held High during FPGA loading operations. Bringing SER_EN Low enables the 2-wire Serial Programming Mode.                                                                                                                                                                                                                                                                                     |

| 20                | VCC      |     | +3.3V/+5V power supply pin.                                                                                                                                                                                                                                                                                                                                                                                         |

### **Absolute Maximum Ratings\***

| Operating Temperature55°C to +125°C                             |

|-----------------------------------------------------------------|

| Storage Temperature65°C to +150°C                               |

| Voltage on Any Pin with Respect to Ground0.1V to $V_{CC}$ +0.5V |

| Supply Voltage (V <sub>CC</sub> )0.5V to +7.0V                  |

| Maximum Soldering Temp. (10 sec. @ 1/16 in.)260°C               |

\*NOTICE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

# **Operating Conditions**

|                 |             |                                                   | AT17CXXX |      | AT17LVXXX |     |       |

|-----------------|-------------|---------------------------------------------------|----------|------|-----------|-----|-------|

| Symbol          | Description |                                                   | Min      | Max  | Min       | Max | Units |

|                 | Commercial  | Supply voltage relative to GND<br>-0°C to +70°C   | 4.75     | 5.25 | 3.0       | 3.6 | V     |

| V <sub>CC</sub> | Industrial  | Supply voltage relative to GND<br>-40°C to +85°C  | 4.5      | 5.5  | 3.0       | 3.6 | V     |

|                 | Military    | Supply voltage relative to GND<br>-55°C to +125°C | 4.5      | 5.5  | 3.0       | 3.6 | V     |

#### **DC** Characteristics

$V_{CC}$  = 5V  $\pm$  5% Commercial/5V  $\pm$  10% Ind./Mil.

| Symbol           | Description                                                 |                     | Min  | Max             | Units |

|------------------|-------------------------------------------------------------|---------------------|------|-----------------|-------|

| V <sub>IH</sub>  | High-level input voltage                                    |                     | 2.0  | V <sub>cc</sub> | V     |

| V <sub>IL</sub>  | Low-level input voltage                                     |                     | 0    | 0.8             | V     |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -4 mA)         |                     | 3.86 |                 | V     |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +4 mA)          | Commercial          |      | 0.32            | V     |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -4 mA)         | la du etal          | 3.76 |                 | V     |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +4 mA)          | Industrial          |      | 0.37            | V     |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -4 mA)         | h dilita - ma       | 3.7  |                 | V     |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +4 mA)          | Military            |      | 0.4             | V     |

| I <sub>CCA</sub> | Supply current, active mode                                 |                     |      | 10              | mA    |

| IL               | Input or output leakage current ( $V_{IN} = V_{CC}$ or GND) |                     | -10  | 10              | μA    |

| 1                |                                                             | Commercial          |      | 0.5             | mA    |

| I <sub>CCS</sub> | Supply current, standby mode                                | Industrial/Military |      | 0.5             | mA    |

#### **DC Characteristics**

$V_{CC}=3.3V\pm10\%$

| Symbol           | Description                                           | Description         |     |                 | Units |

|------------------|-------------------------------------------------------|---------------------|-----|-----------------|-------|

| V <sub>IH</sub>  | High-level input voltage                              |                     | 2.0 | V <sub>CC</sub> | V     |

| V <sub>IL</sub>  | Low-level input voltage                               |                     | 0   | 0.8             | V     |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -2.5 mA) |                     | 2.4 |                 | V     |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +3 mA)    | Commercial          |     | 0.4             | V     |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -2 mA)   |                     | 2.4 |                 | V     |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +3 mA)    | Industrial          |     | 0.4             | V     |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -2 mA)   | N Allian ma         | 2.4 |                 | V     |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +2.5 mA)  | Military            |     | 0.4             | V     |

| I <sub>CCA</sub> | Supply current, active mode                           | I                   |     | 5               | mA    |

| I <sub>L</sub>   | Input or output leakage current (VIN = VCC or GNI     | D)                  | -10 | 10              | μA    |

|                  |                                                       | Commercial          |     | 100             | μA    |

| I <sub>CCS</sub> | Supply current, standby mode                          | Industrial/Military |     | 100             | μA    |

# AT17C/LV512/010

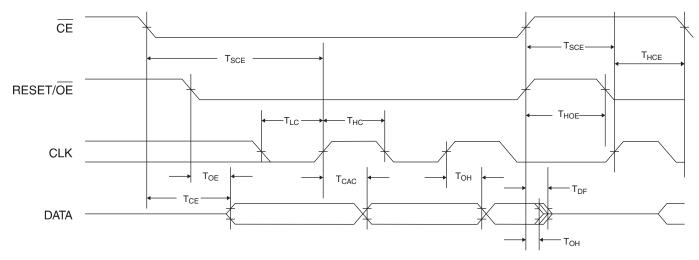

#### **AC Characteristics**

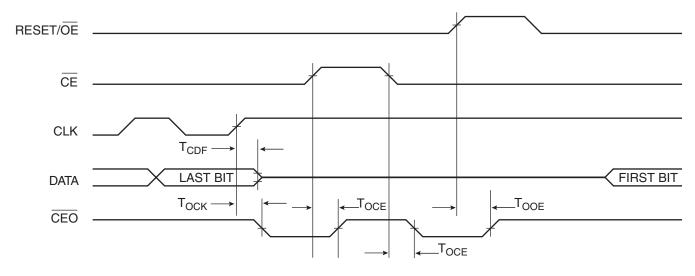

#### **AC Characteristics When Cascading**

#### AC Characteristics for AT17C512/010

|                                 |                                                           | Commercial |     | Industria | Industrial/Military <sup>(1)</sup> |       |

|---------------------------------|-----------------------------------------------------------|------------|-----|-----------|------------------------------------|-------|

| Symbol                          | Description                                               | Min        | Max | Min       | Max                                | Units |

| T <sub>OE</sub> <sup>(2)</sup>  | OE to Data Delay                                          |            | 30  |           | 35                                 | ns    |

| T <sub>CE</sub> <sup>(2)</sup>  | CE to Data Delay                                          |            | 45  |           | 45                                 | ns    |

| T <sub>CAC</sub> <sup>(2)</sup> | CLK to Data Delay                                         |            | 50  |           | 50                                 | ns    |

| Т <sub>ОН</sub>                 | Data Hold From $\overline{CE}$ , $\overline{OE}$ , or CLK | 0          |     | 0         |                                    | ns    |

| $T_{DF}^{()}$                   | CE or OE to Data Float Delay                              |            | 50  |           | 50                                 | ns    |

| T <sub>LC</sub>                 | CLK Low Time                                              | 20         |     | 20        |                                    | ns    |

| T <sub>HC</sub>                 | CLK High Time                                             | 20         |     | 20        |                                    | ns    |

| T <sub>SCE</sub>                | CE Setup Time to CLK (to guarantee proper counting)       | 20         |     | 25        |                                    | ns    |

| T <sub>HCE</sub>                | CE Hold Time from CLK (to guarantee proper counting)      | 0          |     | 0         |                                    | ns    |

| T <sub>HOE</sub>                | OE High Time (guarantees counter Is reset)                | 20         |     | 20        |                                    | ns    |

| F <sub>MAX</sub>                | MAX Input Clock Frequency                                 | 15         |     | 15        |                                    | MHz   |

$V_{CC}$  = 5V  $\pm$  5% Commercial/V\_{CC} = 5V  $\pm$  10% Ind./Mil.

Notes: 1. Preliminary specifications for military operating range only.

2. AC test load = 50 pF.

3. Float delays are measured with 5 pF AC loads. Transition is measured ±200 mV from steady state active levels.

### AC Characteristics for AT17C512/010 When Cascading

$V_{CC}$  = 5V± 5% Commercial/V\_{CC} = 5V ± 10% Ind./Mil.

|                                 |                           |      | Commercial |      | Industrial/Military <sup>(1)</sup> |       |

|---------------------------------|---------------------------|------|------------|------|------------------------------------|-------|

| Symbol                          | Description               | Min  | Max        | Min  | Max                                | Units |

| T <sub>CDF</sub> <sup>(3)</sup> | CLK to Data Float Delay   |      | 50         |      | 50                                 | ns    |

| T <sub>OCK</sub> <sup>(2)</sup> | CLK to CEO Delay          |      | 35         |      | 40                                 | ns    |

| T <sub>OCE</sub> <sup>(2)</sup> | CE to CEO Delay           |      | 35         |      | 35                                 | ns    |

| T <sub>OOE</sub> <sup>(2)</sup> | RESET/OE to CEO Delay     |      | 30         |      | 30                                 | ns    |

| F <sub>MAX</sub>                | MAX Input Clock Frequency | 12.5 |            | 12.5 |                                    | MHz   |

Notes: 1. Preliminary specifications for military operating range only.

2. AC test load = 50 pF.

3. Float delays are measured with 5 pF AC loads. Transition is measured ±200 mV from steady state active levels.

# AT17C/LV512/010

#### AC Characteristics for AT17LV512/010

$V_{CC}=3.3V\pm10\%$

|                                 |                                                           |     | Commercial |     | Industrial/Military <sup>(1)</sup> |       |

|---------------------------------|-----------------------------------------------------------|-----|------------|-----|------------------------------------|-------|

| Symbol                          | Description                                               | Min | Max        | Min | Max                                | Units |

| T <sub>OE</sub> <sup>(2)</sup>  | OE to Data Delay                                          |     | 50         |     | 55                                 | ns    |

| T <sub>CE</sub> <sup>(2)</sup>  | CE to Data Delay                                          |     | 55         |     | 60                                 | ns    |

| T <sub>CAC</sub> <sup>(2)</sup> | CLK to Data Delay                                         |     | 55         |     | 60                                 | ns    |

| Т <sub>он</sub>                 | Data Hold From $\overline{CE}$ , $\overline{OE}$ , or CLK | 0   |            | 0   |                                    | ns    |

| T <sub>DF</sub> <sup>(3)</sup>  | CE or OE to Data Float Delay                              |     | 50         |     | 50                                 | ns    |

| T <sub>LC</sub>                 | CLK Low Time                                              | 25  |            | 25  |                                    | ns    |

| T <sub>HC</sub>                 | CLK High Time                                             | 25  |            | 25  |                                    | ns    |

| T <sub>SCE</sub>                | CE Setup Time to CLK (to guarantee proper counting)       | 30  |            | 35  |                                    | ns    |

| T <sub>HCE</sub>                | CE Hold Time from CLK (to guarantee proper counting)      | 0   |            | 0   |                                    | ns    |

| T <sub>HOE</sub>                | OE High Time (guarantees counter is reset)                | 25  |            | 25  |                                    | ns    |

| F <sub>MAX</sub>                | MAX Input Clock Frequency                                 | 15  |            | 10  |                                    | MHz   |

Notes: 1. Preliminary specifications for military operating range only.

2. AC test load = 50 pF.

3. Float delays are measured with 5 pF AC loads. Transition is measured ±200 mV from steady state active levels

#### AC Characteristics for AT17LV512/010 When Cascading

$V_{CC}=3.3V\pm10\%$

|                                 |                           |      | Commercial |     | Industrial/Military <sup>(1)</sup> |       |

|---------------------------------|---------------------------|------|------------|-----|------------------------------------|-------|

| Symbol                          | Description               | Min  | Max        | Min | Max                                | Units |

| T <sub>CDF</sub> <sup>(3)</sup> | CLK to Data Float Delay   |      | 50         |     | 50                                 | ns    |

| T <sub>OCK</sub> <sup>(2)</sup> | CLK to CEO Delay          |      | 50         |     | 55                                 | ns    |

| T <sub>OCE</sub> <sup>(2)</sup> | CE to CEO Delay           |      | 35         |     | 40                                 | ns    |

| T <sub>OOE</sub> <sup>(2)</sup> | RESET/OE to CEO Delay     |      | 35         |     | 35                                 | ns    |

| F <sub>MAX</sub>                | MAX Input Clock Frequency | 12.5 |            | 10  |                                    | MHz   |

Notes: 1. Preliminary specifications for military operating range only.

2. AC test load = 50 pF.

3. Float delays are measured with 5 pF AC loads. Transition is measured ±200 mV from steady state active levels.

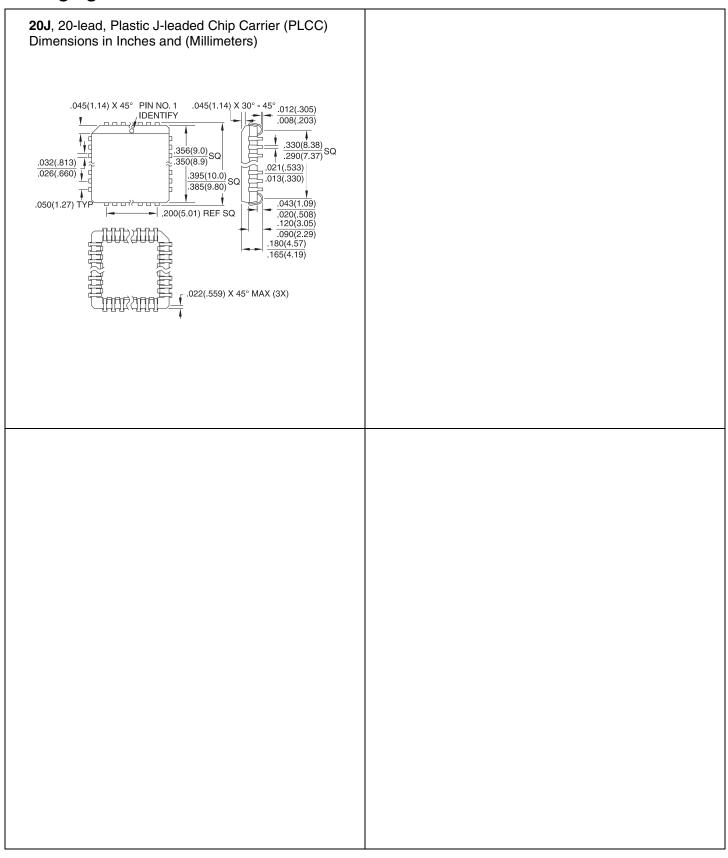

# **Ordering Information – 5V Devices**

| Memory Size | Ordering Code | Package | Operation Range               |

|-------------|---------------|---------|-------------------------------|

| 512K        | AT17C512-10JC | 20J     | Commercial<br>(0°C to 70°C)   |

|             | AT17C512-10JI | 20J     | Industrial<br>(-40°C to 85°C) |

| 1M          | AT17C010-10JC | 20J     | Commercial<br>(0°C to 70°C)   |

|             | AT17C010-10JI | 20J     | Industrial<br>(-40°C to 85°C) |

# **Ordering Information – 3.3V Devices**

| Memory Size | Ordering Code  | Package | Operation Range               |  |  |

|-------------|----------------|---------|-------------------------------|--|--|

| 512K        | AT17LV512-10JC | 20J     | Commercial<br>(0°C to 70°C)   |  |  |

|             | AT17LV512-10JI | 20J     | Industrial<br>(-40°C to 85°C) |  |  |

| 1M          | AT17LV010-10JC | 20J     | Commercial<br>(0°C to 70°C)   |  |  |

|             | AT17LV010-10JI | 20J     | Industrial<br>(-40°C to 85°C) |  |  |

|     | Package Type                                  |

|-----|-----------------------------------------------|

| 20J | 20-lead, Plastic J-leaded Chip Carrier (PLCC) |

# AT17C/LV512/010

# **Packaging Information**

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

Átmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

# *Atmel Configurator Hotline* (408) 436-4118

Atmel Configurator e-mail configurator@atmel.com

#### FAQ

Available on web site

#### © Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

FLEX is a trademark of Altera Corporation.

ORCA is a trademark of Lucent Technologies, Inc.

SPARTAN and Virtex are trademarks of Xilinx, Inc.

Terms and product names in this document may be trademarks of others.

#### **Atmel Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

Atmel Rousset Zone Industrielle 13106 Rousset Cedex France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

Atmel Smart Card ICs Scottish Enterprise Technology Park East Kilbride, Scotland G75 0QR TEL (44) 1355-357-000 FAX (44) 1355-242-743

Atmel Grenoble Avenue de Rochepleine BP 123

38521 Saint-Egreve Cedex France TEL (33) 4-7658-3000 FAX (33) 4-7658-3480

> *Fax-on-Demand* North America: 1-(800) 292-8635 International: 1-(408) 441-0732

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

BBS 1-(408) 436-4309